ÉCOLES D'INGÉNIEUR généralistes du numérique

L2 : Systèmes Numériques Travaux Dirigés

# 1 TD1

# 1.1 Exercice 1

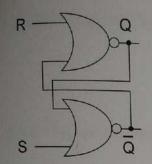

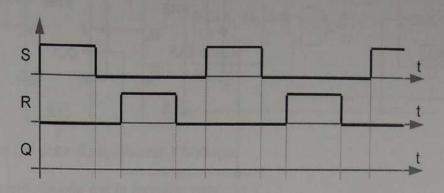

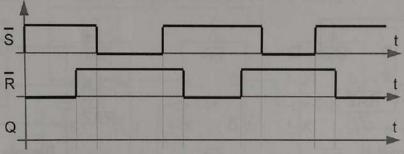

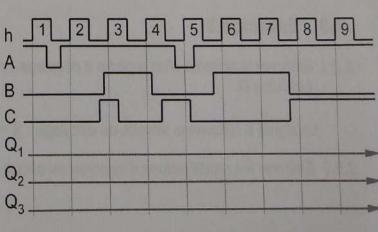

1.1.1 Compléter le chronogramme du circuit ci dessous :

- 1.1.2 Expliquer pourquoi les valeurs R = S = 1 sont interdites.

- 1.1.3 Donner le schéma d'une bascule SR à l'aide de portes logiques combinatoires.

- 1.1.4 Compléter le chronogramme suivant pour cette bascule.

1.1.5 Expliquer pourquoi les valeurs R = S = 0 sont interdites.

# 1.2 Exercice 2

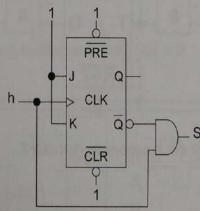

Soit le circuit séquentiel de la figure ci dessous. L'état initial est Q = 1.

1.2.1 Élaborer le chronogramme du signal de sortie S quand l'entrée h reçoit huit impulsions.

# 1.3 Exercice 3

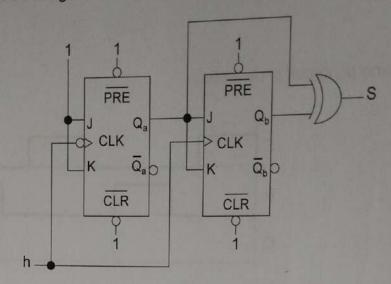

Soit le circuit séquentiel de la figure ci dessous. L'état initial est  $Q_a = Q_b = 0$ .

1.3.1 Élaborer le chronogramme du signal de sortie S quand l'entrée h reçoit 6 impulsions.

# 1.4 Exercice 4

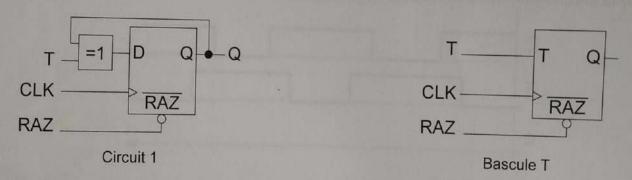

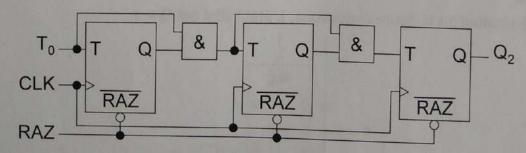

Soit le circuit 1 de la figure suivante :

1.4.1 Décrire le fonctionnement de la sortie Q du circuit 1 en fonction des entrées T, CLK et RAZ.

Nous nommons bascule T le circuit précédent. Soit le circuit de la figure suivante :

1.4.2 Expliquer le fonctionnement du circuit en fonction de l'entrée To

# **Exercice 5**

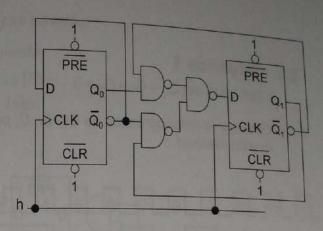

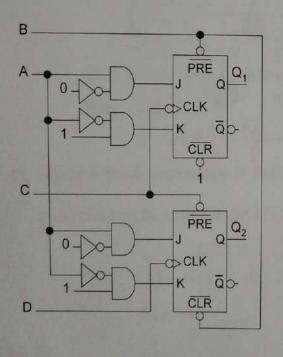

soit le circuit de la figure ci contre :

1.5.1 Déterminer les équations de Do et de D1.

L'état initial est  $Q_0 = Q_1 = 0$ .

- 1.5.2 Tracer le chronogramme de Q0 et de Q1 pour 6 impulsions d'horloge.

- 1.5.3 Déterminer le cycle réalisé par ce circuit. Quelle est la fonction réalisée ?

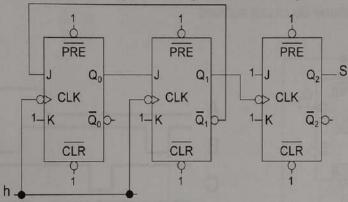

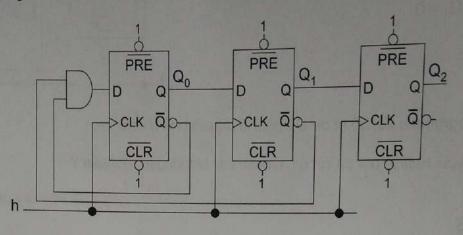

### 1.6 Exercice 6

L'état initial est Q = 0.

1.6.1 Élaborer le chronogramme de Q<sub>0</sub>, Q<sub>1</sub>, Q<sub>2</sub> pour 10 impulsions d'horloge.

1.6.2 Préciser la fonctionnalité du circuit.

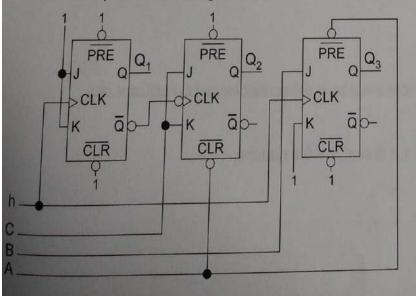

# 1.7 Exercice 7

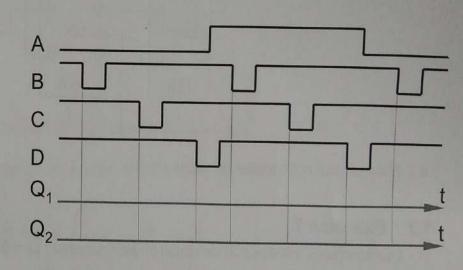

Les conditions initiales (CI) du circuit ci-dessous sont : Qi = 0

1.7.1 Compléter le chronogramme.

# 2.1 Exercice 1

L'état initial est  $Q_0 = Q_1 = Q_2 = 0$ .

2.1.1 Élaborer le chronogramme de Q<sub>0</sub>, Q<sub>1</sub>, Q<sub>2</sub> pour 6 impulsions d'horloge et préciser le cycle de

fonctionnement.

#### Exercice 2 2.2

2.2.1 Compléter le chronogramme du circuit suivant.

#### Exercice 3 2.3

2.3.1 Élaborer le schéma d'un registre à décalage synchrone à trois éléments binaires en utilisant des bascules D.

Le signal S détermine le sens du décalage : S = 1 à droite, S = 0 à gauche.

2.3.2 Élaborer les modifications à apporter au circuit.

# Exercice 4

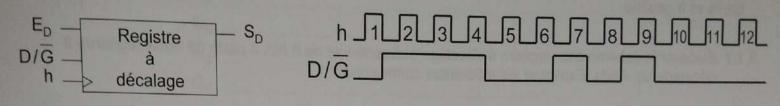

soit le registre à décalage bidirectionnel de 8 bits de la figure suivante.

$D/\overline{G} = 1 \Rightarrow$  décalage à droite,  $D/\overline{G} = 0 \Rightarrow$  décalage à gauche.

À l'état initial le registre contient la valeur binaire du nombre [76]<sub>10</sub>. La position de droite représente le chiffre de poids le plus faible. Un niveau BAS est présent sur l'entrée des données (E<sub>D</sub>). La sortie de données est S<sub>D</sub>.

2.4.1 Déterminer les états du registre en présentant les résultats sous forme de tableau.

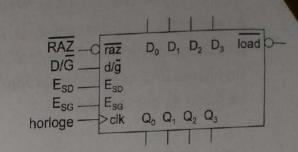

### 3.1 Exercice 1

- Soit le registre à décalage bidirectionnel de quatre bits ci contre.

- L'entrée load active sur niveau bas, le chargement parallèle des entrées D<sub>0</sub>, D<sub>1</sub>, D<sub>2</sub>, D<sub>3</sub>.

- E<sub>SD</sub> et E<sub>SG</sub> sont les entrées de données série respectivement, à droite et à gauche.

3.1.1 Élaborer le schéma d'un registre à décalage bidirectionnel de 8 bits à partir de deux registres à décalage de 4 bits. Expliquer les différentes connexions.

### 3.2 Exercice 2

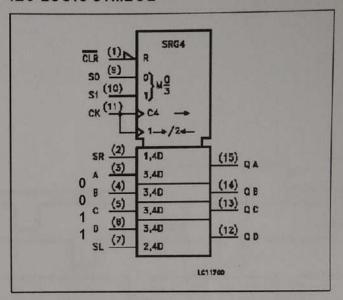

### PIN DESCRIPTION

| PIN No         | SYMBOL   | NAME AND FUNCTION                           |

|----------------|----------|---------------------------------------------|

| 1              | CLEAR    | Asynchronous Reset<br>Input (Active LOW)    |

| 2              | SR       | Serial Data Input (Shift Right)             |

| 3, 4, 5, 6     | A to D   | Parallel Data Input                         |

| 7              | SL       | Serial Data Input (Shift Left)              |

| 9, 10          | S0, S1   | Mode Control Inputs                         |

| 11             | CLOCK    | Clock Input (LOW to<br>HIGH Edge-triggered) |

| 15, 14, 13, 12 | QA to QD | Paralle Outputs                             |

| 8              | GND      | Ground (0V)                                 |

| 16             | Vcc      | Positive Supply Voltage                     |

### IEC LOGIC SYMBOL

#### TRUTH TABLE

| INPUTS |      |    |       |        |       |          |   |   | OUTPUS |     |     |     |     |

|--------|------|----|-------|--------|-------|----------|---|---|--------|-----|-----|-----|-----|

| CLEAR  | MODE |    | CLOCK | SERIAL |       | PARALLEL |   |   |        | QA  | QB  | QC  | QD  |

|        | S1   | SO | CLOCK | LEFT   | RIGHT | Α        | В | С | D      | Ğ   | QD  | 40  | QD  |

| L      | X    | X  | X     | X      | X     | X        | X | X | X      | L   | L   | L   | L   |

| н      | X    | X  | 17    | X      | Х     | X        | Х | X | X      | QA0 | QB0 | QC0 | QD0 |

| Н      | Н    | Н  |       | X      | X     | а        | b | С | d      | a   | b   | С   | d   |

| Н      | L    | Н  | 7     | X      | Н     | X        | X | X | X      | Н   | QAn | QBn | QCn |

| Н      | L    | Н  | 5     | X      | L     | X        | X | X | X      | L   | QAn | QBn | QCn |

| Н      | Н    | L  |       | Н      | X     | Х        | X | X | X      | QBn | QCn | QDn | Н   |

| Н      | Н    | L  | 7     | L      | X     | X        | X | X | X      | QBn | QCn | QDn | L   |

| Н      | L    | L  | X     | X      | X     | X        | X | X | X      | QA0 | QB0 | QCO | QDO |

X: Don't Care : Don't Care

a ~d : The level of steady state input voltage at input A ~ D respactively

QA0 ~ QD0 : No charge

QAn ~ QDn : The level of QA, QB, QC, respectively, before the mst recent positive transition of the clock.

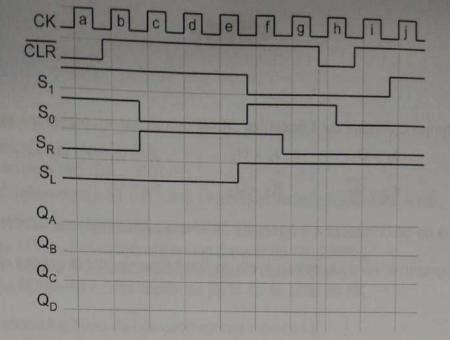

Nous avons A = 0, B = 0, C = 1 et D = 1

3.2.1 Compléter le chronogramme en identifiant les états : décalage gauche, décalage droit, chargement //...

### 3.3 Exercice 3

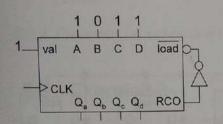

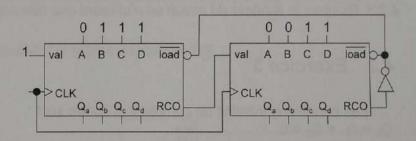

- Les circuits des schémas suivants sont des compteurs de 4 bits.

- La sortie RCO (Register Carry Output) passe à 1 quand l'état du compteur passe à :

Qd Qc Qb Qa = 1111|<sub>2</sub> = F|<sub>16</sub> = 15|<sub>10</sub>.

- D : entrée, Qd : sortie de poids fort. A : entrée, Qa : sortie de poids faible.

- L'entrée LOAD active sur niveau bas le chargement parallèle des entrées A, B, C, D.

- L'entrée VAL active sur «1», le fonctionnement du circuit et sur «0» la mémorisation de l'état en cours.

3.3.1 Donner le cycle de fonctionnement de chacun de ces 2 montages.

# 3.4 Exercice 4

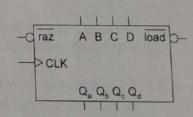

Le compteur synchrone du schéma ci-contre, possède :

- 4 entrées (A, B, C, D) de données parallèles,

- 4 sorties (Qa, Qb, Qc, Qd) de données parallèles,

- 1 commande de chargement parallèle : LOAD active au niveau bas.

Le numéro d'état est : Qd Qc Qb Qa (poids faible Qa, poids fort Qd).

3.4.1 En utilisant l'entrée de chargement //, réaliser le cycle : [0,1,2,3,4,5,6,10,11,12,14,15].

#### 4.1 Exercice 1

Un compteur synchrone composé de 4 bascules JK est donné par les équations suivantes :

$$J_1 = \overline{Q_2} + \overline{Q_3} \cdot \overline{Q_4}$$

$$J_2 = Q$$

$$J_2 = Q_1 \qquad \qquad J_3 = Q_2$$

$$\mathsf{J_4} = \overline{\mathsf{Q_1}} \cdot \mathsf{Q_2} \cdot \mathsf{Q_3} + \mathsf{Q_1} \cdot \overline{\mathsf{Q_2}} \cdot \mathsf{Q_3}$$

$$K_1 = Q_3 + Q_4$$

$$K_2 = \overline{Q_1}$$

$$K_2 = \overline{Q_1}$$

$K_3 = \overline{Q_2}$   $K_4 = \overline{Q_3}$

$$K_4 = \overline{Q_3}$$

- 4.1.1 Élaborer le schéma de ce compteur à 4 bascules JK et des portes logiques INV, NOR et/ou NAND.

- 4.1.2 Tracer son chronogramme, en déduire son cycle de fonctionnement et le graphe d'état associé.

#### Exercice 2 4.2

Soit un compteur synchrone réalisé avec des bascules JK permettant de créer la séquence 1, 2, 5, .7.

- 4.2.1 Élaborer le graphe des états.

- 4.2.2 Élaborer la table des états présents et des états suivants.

- 4.2.3 Élaborer la table de transition de la bascule JK.

- 4.2.4 Simplifier les équations des bascules JK par la méthode de Karnaugh.

- 4.2.5 Réaliser le schéma du circuit en n'utilisant que des portes INV, NOR et/ou NAND.

#### Exercice 3 4.3

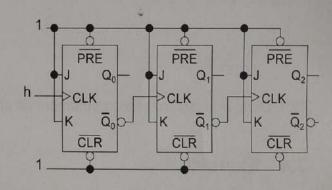

Les conditions initiales du compteur ci contre sont :  $Q_0 = Q_1 = Q_2 = 0$ .

4.3.1 Élaborer le chronogramme des sorties pour 10 impulsions d'horloge.

Chaque bascule possède un temps de propagation (retard) de 8 ns : c'est le temps qui sépare le front déclencheur (entrée CLK) et le changement d'état correspondant (sorties Q2 Q1 Q0)

4.3.2 Déterminer le ou les pires cas de propagation (cas pour lesquels le temps de propagation entre CLK et Q2 et le plus long) et calculer les temps de propagation.

# Exercice 4

4.4.1 Faire le schéma d'un compteur asynchrone modulo 5 à l'aide de bascules JK et de portes logique INV, NOR et/ou NAND.

# Exercice 1

Un système à microprocesseur possède :

- un bus d'adresse de 16 bits (A15,.., A0),

- une bus de données de 8 bits (D7,.., D0),

- des signaux de validation du circuit  $\overline{\mathit{CE}}$  (Chip Enable) et de lecture/écriture  $R/\overline{W}$ .

- Nous souhaitons insérer les mémoires suivantes :

- une mémoire morte M1 de 16K octets implantés à partir de l'@ 2000|16

- une mémoire morte M2 de 8K octets implantés à partir de 8000|16

- une mémoire morte M3 de 4K octets implantés juste après celle de 8K.

- 5.1.1 Élaborer les équations logiques de sélection de ces mémoires.

- 5.1.2 Élaborer les schémas logiques en un nombre minimum de portes (INV, NOR et NAND à 3 entrées

#### 5.2 Exercice 2

Soit un système à base d'un microprocesseur travaillant sur 8 bits de données et 16 bits d'adresse. Il accède à une mémoire de 8 kilos octets lorsque ses adresses sont comprises entre \$6000 et \$7FFF.

- 5.2.1 Élaborer le logigramme du décodage d'adresses en un nombre minimum de portes INV, NOR et/ou NAND.

- 5.2.2 Proposer un schéma à l'aide d'un décodeur réalisant le même décodage d'@.

#### Exercice 3 5.3

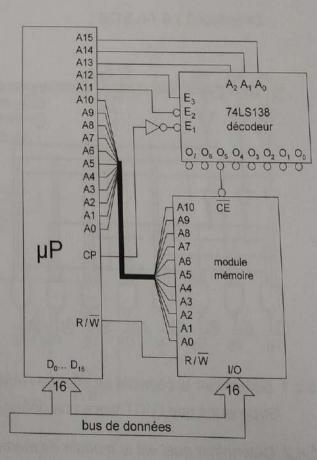

Soit le montage de la figure ci contre. Voir le fonctionnement du décodeur 74LS138 dans l'exercice 4. CP : Clock Pulse.

- 5.3.1 Déterminer le type de la mémoire et sa capacité (en mots et en bits). Justifier.

- 5.3.2 Déterminer la zone adressée par le uprocesseur.

- 5.3.3 Déterminer en base 16 l'adresse qui doit être envoyée par le processeur pour écrire à l'adresse 53 10 de la mémoire.

- 5.3.4 Déterminer en base 16 les valeurs à mettre sur le bus d'adresses et sur le bus de données pour écrire le mot 44|10 à l'adresse 72|10 de la mémoire.

- 5.3.5 Quel est le rôle de l'entrée E1 tel quelle est connectée ?

### 5.4 Exercice 4

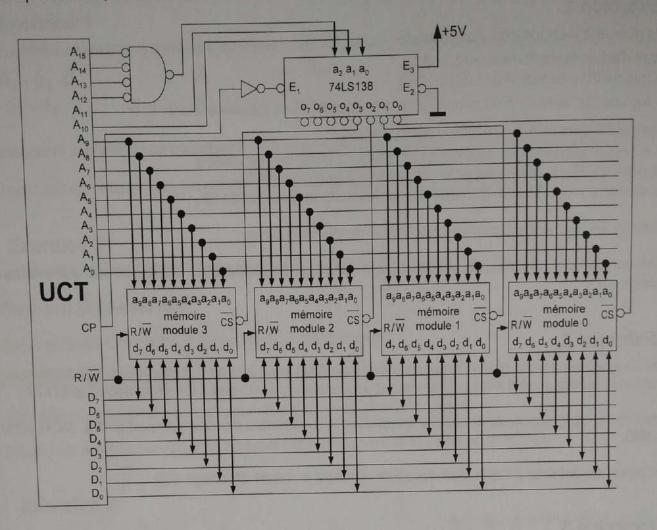

Considérons le schéma suivant : le circuit UCT est l'unité centrale d'un système électronique composé d'un microprocesseur, 4 boîtiers de RAM et un décodeur 74 LS138.

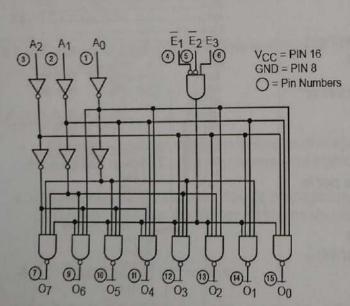

Décodeur 3 x 8 74LS138 :

#### TRUTH TABLE

| INPUTS |                |                |                |    |                | OUTPUTS |    |    |    |    |    |    |    |  |

|--------|----------------|----------------|----------------|----|----------------|---------|----|----|----|----|----|----|----|--|

| E1 I   | E <sub>2</sub> | E <sub>3</sub> | A <sub>0</sub> | A1 | A <sub>2</sub> | 00      | 01 | 02 | 03 | 04 | 05 | 06 | 07 |  |

| Н      | Х              | X              | X              | X  | Х              | Н       | Н  | Н  | Н  | Н  | Н  | Н  | Н  |  |

| X      | H              | X              | X              | X  | X              | Н       | Н  | Н  | Н  | H  | Н  | H  | H  |  |

| X      | X              | L              | Х              | X  | X              | Н       | Н  | H  | H  | Н  | H  | H  | H  |  |

| L      | L              | Н              | L              | L  | L              | L       | Н  | H  | Н  | H  | Н  | H  | H  |  |

| L      | L              | Н              | Н              | L  | L              | Н       | L  | H  | H  | H  | Н  | Н  | Н  |  |

| L      | L              | Н              | L              | H  | L              | Н       | Н  | L  | H  | Н  | Н  | Н  | Н  |  |

| L      | L              | Н              | Н              | H  | L              | Н       | Н  | Н  | L  | H  | H  | Н  | Н  |  |

| L      | L              | Н              | L              | L  | Н              | H       | Н  | H  | Н  | L  | Н  | H  | H  |  |

| L      | L              | Н              | Н              | L  | Н              | H       | Н  | Н  | H  | Н  | L  | Н  | Н  |  |

| L      | L              | Н              | L              | Н  | Н              | H       | Н  | Н  | Н  | Н  | Н  | L  | Н  |  |

| L      | L              | H              | Н              | H  | Н              | H       | Н  | Н  | Н  | Н  | Н  | H  | L  |  |

- H = HIGH Voltage Level

- L = LOW Voltage Level

- X = Don't Care

5.4.1 Déterminer la capacité de chaque RAM.

Supposons que l'UCT lance une opération de lecture des données situées à l'adresse 06A3|16.

- 5.4.2 Déterminer quel est le module de mémoire et quelle est son adresse lue.

- 5.4.3 Déterminer les adresses pour chacun des modules.

# 6 TD6

# Exercice 1

Nous souhaitons fabriquer un plan mémoire à partir de mémoires contenant 2 Ko par boîtier.

- 6.1.1 Indiquer combien de boîtiers sont nécessaires pour obtenir une mémoire de 2 kilos mots de 16 bits et circuits logiques supplémentaires).

- 6.1.2 Indiquer combien de boîtiers sont nécessaires pour obtenir une mémoire de 8 Kilos octets et réaliser le logiques supplémentaires).

- 6.1.3 Indiquer combien de boîtiers sont nécessaires pour obtenir une mémoire de 8 Kilos mots de 16 bits et réaliser le schéma de connexion de ces boîtiers (vous pouvez utiliser, si cela vous semble utile, des circuits logiques supplémentaires).

## 6.2 Exercice 2

Nous souhaitons réaliser un plan mémoire adressable sur 16 bits par un microprocesseur et comprenant :

- 10 Kilos de RAM @ entre \$D800 et \$FFFF,

- 6 Kilos de PROM @ entre \$4000 et \$57FF.

Ces mémoires sont matériellement réalisées à l'aide de boîtiers de 2 Kilos Octets.

- 6.2.1 Déterminer les espaces d'adresses de chaque RAM et chaque PROM.

- 6.2.2 Proposer un schéma réalisant ce décodage en utilisant trois décodeurs à 3 entrées. Un décodeur permettra de sélectionner soit la RAM soit la PROM.

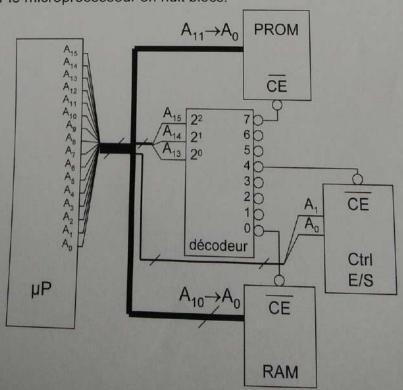

# 6.3 Exercice 3

La figure suivante représente le schéma d'un système à microprocesseur. Le décodeur découpe l'espace adressable par le microprocesseur en huit blocs.

- 6.3.1 Calculer l'étendue de chaque bloc et en déduire les adresses basses et hautes correspondantes.

- 6.3.2 Quelles sont les adresses hautes et basses (vues du microprocesseur) des différents circuits utilisés ? Sont-elles uniques ?

# 6.4 Exercice 4

Soit une mémoire centrale de 2 M octets ou chaque octet est adressable séparément.

- 6.4.1 Calculer l'adresse, en octal du sixième élément d'un tableau dont l'adresse du premier élément est 77\8 et dont tous les éléments sont composés de 16 bits.

- 6.4.2 Calculer, en décimal, le nombre d'Octets précédant l'adresse 77 8.

- 6.4.3 Calculer la taille de cette mémoire en l'exprimant en mots de 16 bits puis en mots de 32 bits.